Shin Megami Tensei Intro

Shin Megami Tensei for the SNES has a really cool intro sequence. I'm not talking about the spinning ATLUS letters or the mode 7 hexagram. I'm not even talking about the creepy and foreboding scenes that interrupt the typing. I'm talking about the code.

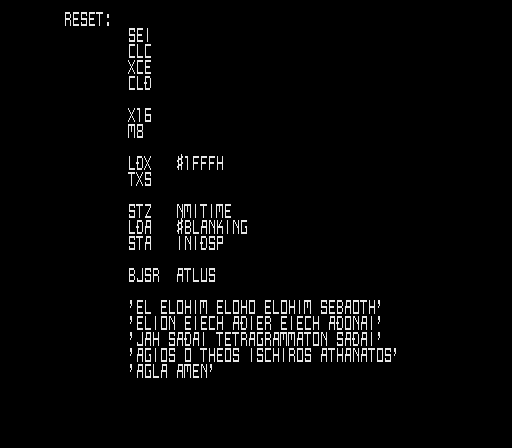

The game's intro sequence shows a terminal-like display with seemingly random letters being typed. To the average person, these would appear as just random letters, but they're actually 65c816 mnemonics. This is SNES code being typed out. And it's not just any SNES code, it's Shin Megami Tensei's own reset routine.

What's a reset routine?

The reset routine is, well, the routine run when the game is reset. For every SNES game in existence, there's a 16-bit address at

There's nothing particularly special about this reset routine. It's actually pretty simple compared to another Shin game I've looked at. I just personally think it's really cool that these guys decided to expose some of the actual code used in the game for the intro.

Almost.

It's not quite the exact same code. But it's pretty close.

The vector itself

Below is the reset code shown in the intro sequence (left) compared to the actual code the game runs (right).

A great start

The very first line is the word "RESET" followed by a colon (:). This is used to define a label in assemblers, but, when the code is assembled, labels and their names don't actually get in. I personally have this label named "Reset", in sentence case, but that's okay! There's no wrong answer here! I'll give them the point.

Following that are 4 instructions that are exactly correct:

SEt Interrupt flag. This tells the CPU to not respond to any interrupt request from the IRQ line.

CLear Carry flag. This clears the carry flag, exactly as the name implies.

eXchange Carry and Emulation flags. Emulation? Yes. Technically, the SNES is an emulator. An emulator for what you ask? Why, the 6502 of course! When the Western Design Center created the 65c816 (the chip the SNES Ricoh 5A22 is based on), they wanted it to be backwards compatible enough that you were meant to literallyYes, literally. While literally screaming

"AAAAAAAAAAAAARRRRRRRRRRRGGGGGGGGGGGG!!!!!!!!!!!!!!!!!!" just rip out the 6502 from whatever machine you were using and put a next-gen processor in its socket.

The newer chip has more advanced capabilities and modes of operation, but requiring configuration before it can behave as the lesser chip would make it an unsuitable replacement. So, by design, whenever a reset is triggered, the 65c816 and its variants always start in 6502 emulation mode. The processor status register only has 8 bits visible to the programmer; the 9th bit, the emulation flag, is hidden. The only way to affect the flag is to swap it with the carry flag.

CLear Decimal flag. The 6500 series is able to perform arithmetic with a more human-friendly system called "Binary Coded Decimal". Since this mode is immediately disabled, I'm not going to explain it.

Technically correct

Or is it? 🤨

This is almost certainly an assembler-specific mnemonic for exactly what I have on the right: ResEt Processor flags. In this case, the only flag being reset is bit 4, the index register flag also known as

SEt Processor flags. This time, the 5th bit (the

I call her LIFO

LoaD X register, and the # means immediate addressing; i.e. it will use the operand as a literal value instead of an address. In this case, that value is H is used to indicate that a value is to be interpreted as hexadecimal. This wasn't unheard of for assemblers of the time, but it is inferior to the $ prefix. At least if you ask me. By reading this blog, you are hereby asking me.

Transfer X to Stack pointer. The value we just loaded is what's being transfered here. This means that the top of the stack is now pointing to that location in memory (

Divergence

STore Zero to, and it's writing to some address that has been named

But what's this? The actual instruction the game uses is an STore Accumulator to, after using LoaD Accumulator with

What gives? They made their real code take more time and space than the code in their intro sequence. While it's completely inconsequential, it's still confounding. Someone was clearly aware of this slightly better code, but apparently someone else (or maybe the same guy) wanted to be a contrarian?

Back on track

WTF

Now, out of nowhere, we have a huge chunk of code that's completely missing from the intro. Maybe it was omitted because it was boring, or maybe it wasn't written yet. This code sets some flags and reads RAM for a signature that the game uses to check for a soft reset. RAM decays, but if it only lacks power for a short period of time, it will stay in tact. So here, the game is looking for the phrase programming by cozy! in Work RAM, and, if it finds it, it will skip the animated logo.

Even more wtf

Big Jump to SubRoutine, which would be a jump to code specified by a 24-bit address. The actual letters normal people use are Jump to Subroutine Long.

The routine in game is something named

I think it's safe to assume they're the same thing.

God is Good

The chant at the bottom seems like complete gibberish, as if someone were speaking in tongues, but it has an actual traceable source! The Grimoire of Armadel is a book by some French guy in the 1600s, and it contains this text on page 19. The linked printing of the text contains a translation of the text, and while it isn't gibberish, it doesn't really mean anything.

Most of the words are actually Hebrew names for God. The latter lines contain Greek describing God as powerful. The agla in the final line is a Hebrew acronym meaning "God is strong forever!"

Unfortunately, no matter how hard I try, I cannot get this chant to assemble into a ROM.